## EE 435 Homework 4 Spring 2024

Due Wednesday Feb 28

## Problem 1 and 2

The model parameters  $\mu$ ,  $C_{OX}$ ,  $V_{TH}$  and  $\lambda$  are widely used in analytical formulations of the performance of analog circuits. These parameters are used to characterize how MOS transistors operate in the square-law model of the transistor.

When operating in the saturation region, the square-law model for the drain current of transistors can be expressed as

$$I_{D} = \begin{cases} \frac{\mu_{n}C_{OX}W}{2L} \big(V_{GS} - V_{THn}\big)^{2} \big(1 + \lambda_{n}V_{DS}\big) & \text{for } n - \text{channel devices} \\ -\frac{\mu_{p}C_{OX}W}{2L} \big(V_{GS} - V_{THp}\big)^{2} \big(1 - \lambda_{p}V_{DS}\big) & \text{for } p - \text{channel devices} \end{cases}$$

Though this square-law formulation is a simplification, it gives reasonable results that can be used for much of the design process. Better and more comprehensive models, such as the BSIM models, are then used in computer simulations to more accurately predict performance and for refining the design to meet target specifications. The BSIM models, however, are not analytically tractable and thus unsuitable for analytical formulations. Though intermediate models that are more accurate than the square-law models and less comprehensive than the BSIM models exist, there is little evidence of analytical tractability for models with complexity beyond that of the square-law model.

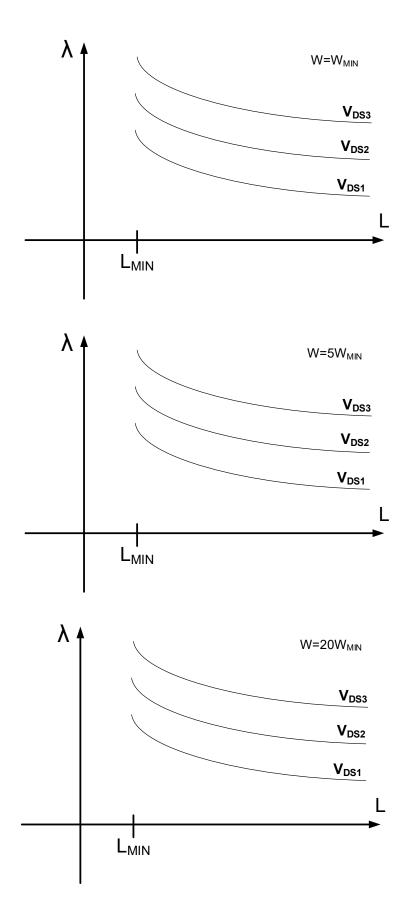

Many analog circuits are quite sensitive to the parameter  $\lambda$  in the square-law model. Unfortunately, the parameter  $\lambda$  is quite sensitive to device dimensions and operating point. As such, a table or plot of  $\lambda$  parameters is useful when using the square-law model for predicting the performance of many analog circuits based upon the square-law model.

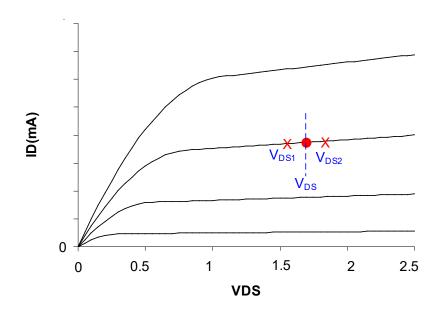

Generate plots of  $\lambda$  for both n-channel and p-channel transistors in the 0.18µm CMOS for different lengths and for three different values of W and for three different values of  $V_{DS}$  as shown below. Comment on how  $\lambda$  varies with device dimensions and operating points. When determining  $\lambda$ , assume that the devices are modeled by the BSIM model which is embedded in the PDK file used in SPECTRE. Extract  $\lambda$  at a given operating point by taking two measurements (simulation results) of the drain current at values of  $V_{DS}$  slightly above and slightly below the target  $V_{DS}$  value on a constant  $V_{GS}$  locus as shown in the plot below. This is likely how you extracted the parameter  $\lambda$  in EE 330. The length should vary between  $L_{MIN}$  and  $20L_{MIN}$  and the VDS values should be from slightly above  $V_{EB}$  to 2.5V.

Page 3 of 6

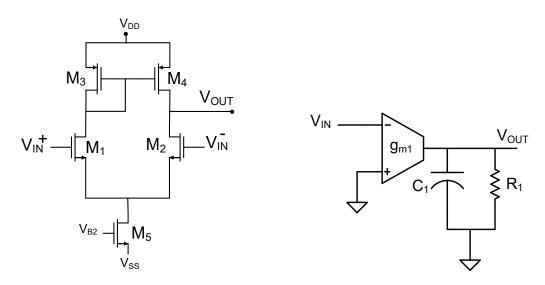

**Problem 3** Consider the 5T op amp configured used as a transconductance amplifier in the circuit shown below. Assume the op amp is designed in a 0.18 $\mu$ m ON CMOS process with V<sub>DD</sub>=1.2V, V<sub>SS</sub>=-1.2V, L=2 $\mu$ m and V<sub>EB</sub>=100mV for all transistors, and the power in the op amp is 1mW. Assume  $\lambda$ =.01V<sup>-1</sup>.

- a) What is  $W_1$ ?

- b) What is the quiescent voltage at the source of  $M_1$ ?

- c) Obtain an expression for the small signal voltage gain of the OTA circuit in terms of the small-signal parameters  $g_{m1}$ ,  $R_1$ , and  $C_1$ .

- d) Numerically determine and plot the small signal frequency dependent voltage gain if R<sub>1</sub>=50K and C<sub>1</sub>=40pF

- e) Determine the 3dB bandwidth

- f) How does the 3dB bandwidth change if the power in increased by 20% by changing  $V_{\rm B2}$ ?

Problem 4 Assume an operational amplifier has gain given by the expression

$$A(s) = \frac{10^9}{(s+5)(s+10^4)}$$

and is used in a standard feedback configuration where the gain

with feedback is given by the expression  $A_{FB}(s) = \frac{A(s)}{1 + A(s)\beta}$ .

- a) What is the pole spread in the open-loop amplifier

- b) What is the pole Q if  $\beta$ =0.1

- c) How much overshoot in the magnitude of the feedback gain will occur if  $\beta$ =0.5

- d) What is the minimum closed-loop dc gain that can be achieved if there is to be no ringing in the step response

- e) Assume the low frequency open loop pole at 5rad/sec can be moved without changing the dc gain or the second pole of the op amp. What is the minimum movement of the pole that is necessary to have no ringing in the step response of the closed loop amplifier is  $\beta$ =1.

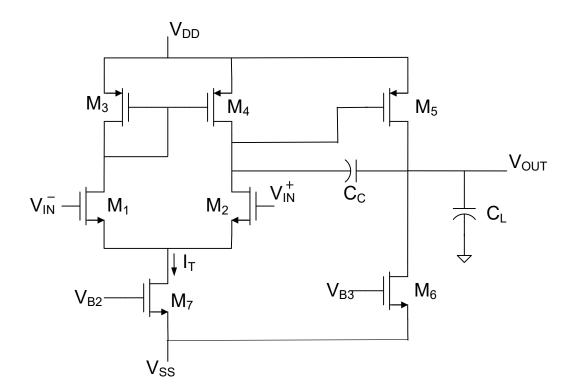

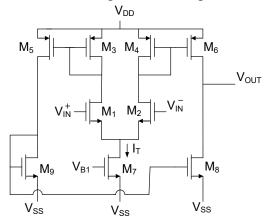

Problem 5 Consider the current-mirror op amp shown below. Assume  $V_{DD}=1.2V$  and  $V_{SS}=-1.2V$ .

- a) Size the devices if the excess bias of all transistors is to be 150 mV, the mirror gain of the two p-channel mirrors is to be 20, the n-channel mirror gain is 1, and the total power dissipation is 10mW.

- b) If the amplifier designed in part a) is driving a 10pF load, determine the dc voltage gain and the GB of this amplifier.

- c) Determine the transconductance gain of the amplifier designed in part a).

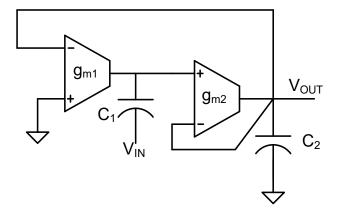

Problem 6 Consider the following circuit where the OTAs are assumed to be ideal.

- a) Obtain the transfer function  $T(s) = \frac{V_{OUT}}{V_{IN}}$

- b) Determine the poles of the circuit in terms of the small-signal parameters  $g_{m1}, g_{m2}, C_1$  and  $C_2$ .

- c) If  $g_{m1}=g_{m2}=10^{-8}$  A/V,  $C_2=500$  pF and  $C_1=50$  pF, plot the magnitude of the transfer function T(s) versus frequency

**Problem 7** Consider the polynomial  $D(s) = s^2+1500s+3000$ . It was pointed out in the lecture that when a second-order polynomial has widely separated poles on the negative real axis that the high-frequency pole can be closely approximated by

considering only the  $s^2$  and s terms and the low frequency pole can be closely approximated by considering only the constant and the s-term in this expression. Compare the actual roots and the approximate roots for D(s) and comment on how much error is introduced by using this approximation approach.

Problem 8 and 9 Consider the 7-T op amp where all transistors are sized for  $V_{EB}$ =0.1V with a power dissipation of 2mW split evenly between the first and second stage and where Miller compensation is used. Assume this is designed in a 0.18μm CMOS process with  $V_{DD}$ =1.2V,  $V_{SS}$ =-1.2V, and  $C_{L}$ =100fF. Assume the process is characterized by parameters  $\mu_n C_{OX}$ =300 $\mu$ AV<sup>-2</sup>,  $V_{THn}$ =0.5V,  $V_{THp}$ =-0.5V,  $V_{THp}$ --0.5V,  $V_{TH$

- a) Determine  $V_{B2}$  and  $V_{B3}$

- b) Determine W/L for all transistors

- c) What is the dc gain of this operational amplifier?

- d) Determine  $C_C$  if the feedback amplifier is to have a closed-loop pole Q of 0.707 when  $\beta$ =0.2.

- e) What is  $g_{m5}$ ?